# DS modulator for digital wireless architecture

By Sirma sirma

## ΣΔ Modulator for Digital Wireless Architecture: A review

Sirmayanti Sirmayanti<sup>1,2</sup>

The State Polytechnic of Ujung Pandang,

Telecommunication Study Program

Makassar, Sulawesi Selatan, Indonesia

Abstract— This paper studies Sigma-Delta  $(\Sigma\Delta)$  technique to embed a complex modulation scheme such as orthogonal frequency division multiplexing (OFDM) into a single 'on'-'off' bit stream operating the carrier frequency. The amplitude of the signal is related to the pulse widths and the phase to the pulse position. This paper concentrates on all digital upconverter structures of  $\Sigma\Delta$  modulator architecture. The binary nature of their output removes the need for analog components in the upconversion chain. Their outputs can be used directly to drive the switch mode power amplifier (SMPA) for high efficiency operation.

#### I. INTRODUCTION

Research in green communications is addressing energy efficiency of the telecommunications sector, to reduce the cost of emissions and the world's carbon footprint. Software-defined Radio (SDR) is gaining popularity because digital circuits provide software controllable features such as coding/decoding, modulation/demodulation, feltering, mixing, and power control [1-3]. The trend in SDR is to push the digital part close to the antenna part to remove analog selection mechanism 12 However, traditional SDR still requires some analog components such as analog-to-digital and digital-to-analog converters (ADC/DAC), up/down converters, RF selectivity and RF amplification.

Digital wireless transmission is related to all-digital transmitter design with fully digital components. To move towards all-digital wireless transmitters, the elimination of analog components is required. Various signal processing innovations are now being proposed by the research community to this end. If such solution can be found then integration on to low cost digital *Silicon* Complementary Metal Oxide Semiconductor (Si CMOS) technology will produce major reduction in both size, cost and energy consumption.

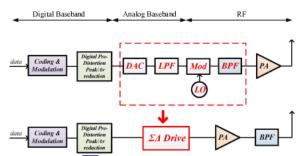

A traditional wireless transmitter architecture is described in Fig. 1 (top). It consists of analog components such as ADC/DAC, filters, a modulator (Mod), and a local oscillator (LO). A new wireless transmitter architecture in Fig. 1 (bottom) has introduced the use of a digital  $\Sigma\Delta$  structure which replaces the analog components from the traditional transmitter architecture. Removal of the analog components also removes many analog problems, such as gain-phase imbalance and carrier leakage of the quadrature modulator, the need for an RF synthesiser and the need for wideband matching of the low-pass filters (LPF).

Mike Faulkner<sup>2</sup>

<sup>2</sup>Victoria University

School of Engineering and Science

Melbourne, Victoria, Australia

$\Sigma\Delta$  techniques are most well known for their use in ADC and DAC structures. These schemes are almost entirely based on the conversion of low-pass signals. The best known early application of  $\Sigma\Delta$  DACs was for the compact disc (CD) player [4]. Here the sample rate was increased to red 19 the (quantisation) noise power spectral density which was shaped by a first order filter to further reduce the noise in the lower frequencies. In this way high fidelity signal reproduction was possible from DAC's of reduced resolution.

Figure 1.  $\Sigma\Delta$  23 cture can potentially replace the analog components of the traditional wireless architecture (top). A potential future wireless transmitter architecture (bottom).

The study of  $\Sigma\Delta$  modulator architecture is reviewed in this paper. Recent research is now applying  $\Sigma\Delta$  techniques to band-pass signals such as found in radio frequency transceivers [5]. There are a number of challenges to developing such schemes. First, the carrier frequency is of the same order as the sample rate; secondly the bandwidth, EVM and spectral mask of any transmitted RF signal must be met; and thirdly, any design must be realisable in today's silicon technology. These three factors are all inter-related and form a complex trade-off between performance, complexity and energy consumption. This paper concentrates on all digital upconverter structures. The binary nature of their output removes the need for analog components in the upconversion chain. Their outputs can be used directly to drive the SMPA (Class-S or Class-D) for high efficiency operation [6].

#### II. BAND-PASS $\Sigma\Delta$ ARCHITECTURE

Band-pass  $\Sigma\Delta$  modulator is proposed as a possible solution suitable for RF digital transmitter design using SMPA. A band-pass  $\Sigma\Delta$  modulator generates a digital pulse

2014 Makassar International Conference on Electrical Engineering and Informatics (MICEEI) Makassar Golden Hotel, Makassar, South Sulawesi, Indonesia

26-30 November 2014

train and shapes the quantisation noise which is then fed to the switched amplifier.

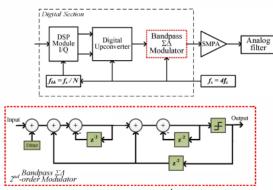

Figure 2. Band-pass  $\Sigma\Delta$  Architecture in [6].

Figure 3. BPF for RF PWM/PPM output.

It is possible to avoid the analog processing by doing the up-conversion in DSP and replacing the band-1 ss  $\Sigma\Delta$  1-bit A/D with a band-pass  $\Sigma\Delta$  1-bit D/A as shown in Fig. 4 [7]. The DSP module generates the input signal as an I and Q baseband [7] al. The I-Q baseband is interpolated to a higher sampling frequency before digital up-conversion. The up-conversion operation multiplies the I-Q baseband signals with the pulse sequences of 1,1,-1,-1,... and -1,1,1,-1,... respectively. The two signals are summed together and fed directly into the band-pass  $\Sigma\Delta$  modulator, which generates the digital data streams for the [11] A. The band-pass  $\Sigma\Delta$  transmitter architecture operates at a sampling frequency that is four times the RF carrier frequency. The high clock rate ( $f_{clock}$ ) will require substantial power consumption which reduces efficiency [8].

Figure 4. The band-pass  $\Sigma\Delta$  (2<sup>nd</sup> order) architecture proposed in [7].

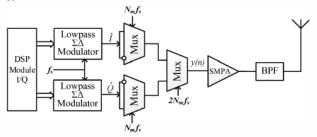

A digital method proposed in [9], implements the bandpass  $\Sigma\Delta$  technique using a combination of two low-pass  $\Sigma\Delta$  modulators and upconverters, Fig. 5. Each baseband I and Q signal has its own low-pass  $\Sigma\Delta$ . The three multiplexer units (Mux) implement a quadrature modulator that up-converts the quantised one bit  $\hat{I}$ - $\hat{Q}$  signals to RF at a carrier frequency  $f_c$ .

$$y_{RF}(n) = \hat{Q}\sin\left(2\pi n \frac{f_c}{f_{clock}}\right) + \hat{I}\cos\left(2\pi n \frac{f_c}{f_{clock}}\right)$$

(1)

when  $f_{clock} = 4f_c$  the above sequences become  $\sin(2\pi n \frac{f_c}{f_{clock}}) = 0,1,0,-1,0,1,...$  (2)

$$\cos\left(2\pi n \frac{f_c}{f_{clock}}\right) = 1, 0, -1, 0, 1, 0 \dots$$

(3)

The summation of the sequences is trivial and can be performed in a multiplexer (Mux), since one term is always 0

Figure 5. The band-pass  $\Sigma\Delta$  (two low-pass  $\Sigma\Delta$ s) architecture proposed in [9].

It is possible to generate RF signals with carrier frequency  $f_c > 1$  GHz using off-the-shelf multiplexer devices. However it is harder to achieve GHz sample rates  $(f_s)$  for the DSP and  $\Sigma\Delta$  modulators without resorting to application-specific integrated circuit (ASIC) implementation [10]. The achievable bandwidth is proportional to sampling frequency  $f_s$ .

It is difficult to get high sampling rates on the  $\Sigma\Delta$  D/A's because of the feedback path. The filtering and quantisation must all be completed within the latency 6 one clock period. Frappé *et al.* [11] developed an ASIC using Borrow-Save arithmetic, non-exact quantisation and a multiphase-clock to complete all calculations of a 3<sup>rd</sup>-order  $\Sigma\Delta$  filter in 250 *ps* (pico second). A signal bandwidth of 50 MHz was obtained.

#### III. POLAR $\Sigma\Delta$ ARCHITECTURE

Polar  $\Sigma\Delta$  techniques operate on the polar (amplitude A(t) and phase  $\Phi(t)$ ) signals rather than the more normal I-Q representation. The polar  $\Sigma\Delta$  structure was proposed in [12-15] where the aim was to reduce the switching activity and also to eliminate the need for analog components.

Fig. 6 shows a polar  $\Sigma\Delta$  architecture consisting of a lowpass 1-bit  $\Sigma\Delta$  modulator using a phase modulated clock and a gated PA [15]. The envelope input signal A(t) represents the 20 rage value of the 'on'-'off' period of the square wave signal at the 15 put of the low-pass  $\Sigma\Delta$  modulator. The phase information is represented by the zero-crossing timing of the RF carrier. The PA is operated in saturated mode (for best performance with a Class-C structure [16]), and the input waveforms are square waves. This scheme implements burstmode modulation where the  $\Sigma\Delta$  modulator switches the square wave RF input signal 'on' or 'off' [15].

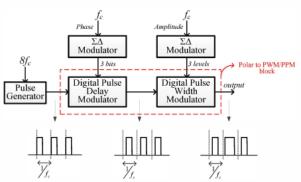

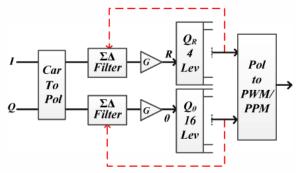

Keyzer *et al.* in [13], the architecture consists of the two  $\Sigma\Delta$  modulators (each modulator generates a pulse train representing the phase and amplitude signals respectively), followed by up-conversion blocks to perform PWM and PPM generation, Fig. 7. The amplitude is quantised into three

2014 Makassar International Conference on Electrical Engineering and Informatics (MICEEI) Makassar Golden Hotel, Makassar, South Sulawesi, Indonesia 26-30 November 2014

levels and the phase is quantised into eight levels. A digital pulse delay mod to racts on an input periodic pulse train with period of  $f_c$  and pulse width  $\frac{1}{8f_c}$  to produce an output phase modulated pulse train. This is then followed by a pulse expander to change the phase width. The structure limits the number of pulses per period to one and there is often no switching pulse when the input signal is small. Therefore, it should have good efficiency; however there is a bandwidth penalty.

Figure 6. The polar  $\Sigma\Delta$  based burst-mode architecture proposed in [15].

Figure 7. The polar  $\Sigma\Delta$  architecture proposed in [13].

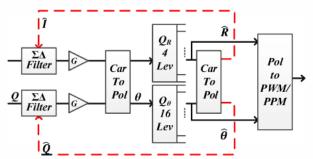

Bassoo *et al.* in [14] investigated the polar  $\Sigma\Delta$  structure which is shown in Fig. 8. The input signal of *I-Q* complex baseband is converted to polar representations,  $R=\sqrt{I^2+Q^2}$  and  $\theta=\tan^{-1}\left(\frac{Q}{I}\right)$ . Low-pass  $\Sigma\Delta$ 's are used to independently quantise the R (amplitude) and the  $\theta$  (phase) signals respectively. The R value is quantized into 4 distinct levels while  $\theta$  is 21 intized to 16 levels uniformly distributed between 0 to  $2\pi$ . The output of these quantisers is fed back to their appropriate  $\Sigma\Delta$  filter. The quantized signal is also passed through to a 'Polar to PWM/PPM' block converter to 1 nerate the appropriate pulse waveform. The pulse train output of the 'Polar to PWM/PPM' block feeds to the SMPA and BPF.

Normally, the  $\Sigma\Delta$  filters update the pulse width and position every whole number of cycles of the carrier frequency for half cycles if a bridge amplifier is used). The  $\Sigma\Delta$  filters for the phase signal must be modified to handle the phase wrap-around. The polar components have a wider bandwidth than the I-Q components, and this limits modulation bandwidth of this structure hence the effective oversampling rate is reduced. Besides that, the conversion process of I-Q complex baseband from Cartesian format to

polar format is a nonlinear process which causes some of the quantisation noise to fold back into the band of interest and hence it cannot be filtered out [17].

Figure 8. Polar  $\Sigma\Delta$  Architecture proposed in [14].

Another problem is unwanted spectral components which arise when baseband polar signals are upconverted to RF using PWM/PPM techniques. The 'Polar to PVM/PPM' block upconverts the signal to RF with quantised amplitude and phase. The amplitude of the RF is controlled by the pulse width and the phase of the RF is controlled by the pulse position. In the PPM process, a cringe in phase is represented by a change in position and the pulse edge must occur on the digital timing grid. This process eventually leads to amplitude modulation (AM) as a pulse is swallowed whenever there is a change in quantisation level. Recently, Bassoo et al. in [14] has established that the dominant distortions are the image and harmonic components generated in the PPM circuit ('Polar to PWM/PPM' block).

#### IV. CARTESIAN $\Sigma\Delta$ ARCHITECTURE

The authors in [18, 19] realised that Cartesian  $\Sigma\Delta$  upconverters are an improvement over the polar  $\Sigma\Delta$  modulator in [14], with regard to solving the bandwidth expansion problems and reducing switching activity. Fig. 9 shows the comparison plot between polar and Cartesian  $\Sigma\Delta$ s using an OFDM signal. The output spectrum and ACP versus signal level are compared. The Cartesian  $\Sigma\Delta$  has better noise shaping with a better null around the band of interest and lesser noise than the polar  $\Sigma\Delta$  (Fig. 10(a)). Fig. 10(b) shows the Cartesian  $\Sigma\Delta$  has at 8 ast 10 dB less ACP, over a wide dynamic range of input signal levels, compared to the polar  $\Sigma\Delta$ .

The proposed Cartesian  $\Sigma\Delta$  structure can be seen in Fig. 10. It consists of MOD2 low-pass  $\Sigma\Delta$ s [5] for the Cartesian I and Q input signals. After  $\Sigma\Delta$ -filtering, the I and Q signals are then converted to polar co-ordinates  $[R, \theta]$  and separately quantised in the  $Q_R$  and  $Q_\theta$  blocks resulting into  $[\widehat{R}, \widehat{\theta}]$ . The quantised in the  $Q_R$  and  $Q_\theta$  blocks resulting into  $[\widehat{R}, \widehat{\theta}]$ . The efficiency (by reducing the number of switching edges) at the expense of a degraded spectrum [20]. The output of the suntisers is converted back to Cartesian co-ordinates,  $[\widehat{I}, \widehat{Q}]$  (removing bandwidth expansion [20]) and fed as feedback to the  $\Sigma\Delta$  filters. The outputs of both quantisers are also

2014 Makassar International Conference on Electrical Engineering and Informatics (MICEEI) Makassar Golden Hotel, Makassar, South Sulawesi, Indonesia

26-30 November 2014

upconverted to RF using PWM/PPM techniques in the 'Polar to PWM/PPM' block.

Figure 9. (a) Normalized spectrum of OFDM and (b) ACP for Cartesian  $\Sigma\Delta$  and polar  $\Sigma\Delta$  modulator [18].

Figure 10. Cartesian  $\Sigma\Delta$  Architecture [21].  $\Sigma\Delta$  filtering is in Cartesian with quantisation in polar.

The proposed quantiser used an even quantisation technique where the three-level-waveform at the output is based on pulses with an even number of clock period{18, 21, 22]. The quantised amplitudes,  $\hat{R}$ , of the RF signal are calculated by changing the pulse widths in increments of two clock periods. However, this leads to a potential coarse quantisation at low signal levels, as the minimum pulse width in the even quantisation scheme is two clock periods.

Furthermore, while reducing the bandwidth expansion, the Cartesian  $\Sigma\Delta$  model may still cause unwanted spectral components due to the 'Polar to PWM/PPM' block. The most relevant work to the aims of the proposed research was presented in [21]. It showed that in a single carrier environment, an increase in offset frequency increases the unwanted spectral components. The image and  $3^{rd}$  order harmonic components are the dominant distortions. The PPM block was shown to be responsible for these distortions, but no solutions were proposed.

#### V. CONCLUSION

RF up-conversion using  $\Sigma\Delta$  techniques is a potential replacement to traditional techniques using analog circuits. The all-digital output creates a number of noise and distortion products. Techniques to address these problems have been discussed.

#### REFERENCE

- [1] J. Mitola and G. Q. Maguire, Jr. (1999) Cognitive radio: making software radios more personal. *IEEE Personal Comm.*, 13-18.

- [2] J. Vankka, Digital synthesizers and transmitters for software radio: Springer, 2005.

- [3] F. M. Ghannouchi, "Power amplifier and transmitter architectures for software defined radio systems," *IEEE Circuits and Systems Mag.*, vol. 10, pp. 56-63, 2010.

- [4] R. Schreier, G. C. Temes, and J. Wiley, Understanding delta-sigma data converters vol. 74: IEEE press Piscataway, NJ, 2005.

- [5] R. Schreier and M. Snelgrove, "Bandpass sigmadelta modulation," *Electronics Letters*, vol. 25, pp. 1560-1561, 1989.

- [6] S. P. Stapleton, "High efficiency RF power amplifiers using bandpass delta-sigma modulators," *Agilent Technologies, Inc.*, pp. 1-22, 2003.

- [7] J. Keyzer, J. Hinrichs, A. Metzger, M. Iwamoto, I. Galton, and P. Asbeck, "Digital generation of RF signals for wireless communications with band-pass delta-sigma modulation," in *IEEE MTT-S International Microwave Symp. Digest*, , 2001, pp. 2127-2130.

- [8] C. Jinsung, Y. Jounghyun, Y. Jinho, K. Jingook, C. Jeonghyun, D. Kang, et al., "A Delta Sigma-Digitized Polar RF Transmitter," *IEEE Transactions on Microwave Theory and Tech.*, vol. 55, pp. 2679-2690, 2007.

- [9] M. Helaoui, S. Hatami, R. Negra, and F. M. Ghannouchi, "A novel architecture of delta-sigma modulator enabling all-digital multiband multistandard RF transmitters design," *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 55, pp. 1129-1133, 2008.

- [10] A. Frappe, B. Stefanelli, A. Flament, A. Kaiser, and A. Cathelin, "A digital DS RF signal generator for mobile communication transmitters in 90nm CMOS," in *IEEE*, *Radio Frequency Integrated Circuits Symp.*, *RFIC*. 2008, pp. 13-16.

- [11] A. Frappé, A. Flament, B. Stefanelli, A. Kaiser, and A. Cathelin, "An all-digital RF signal generator using high-speed modulators," *IEEE Journal of Solid-State Circuits*, vol. 44, pp. 2722-2732, 2009.

- [12] V. K. Parikh, P. T. Balsara, and O. E. Eliezer, "All digital-quadrature-modulator based wideband wireless transmitters," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 56, pp. 2487-2497, 2009.

- [13] J. Keyzer, R. Uang, Y. Sugiyama, M. Iwamoto, I. Galton, and P. Asbeck, "Generation of RF pulsewidth modulated microwave signals using delta-sigma modulation," in *IEEE MTT-S International, Microwave Symposium Digest*, 2002, pp. 397-400.

2014 Makassar International Conference on Electrical Engineering and Informatics (MICEEI) Makassar Golden Hotel, Makassar, South Sulawesi, Indonesia 26-30 November 2014

- [14] V. Bassoo, A. Mustafa, and M. Faulkner, "Distortion arising from polar to PWM/PPM conversion in an all digital upconverter for switching rf power amplifier," in *IEEE MTT-S International*, *Microwave Symposium Digest*, MTT'09., pp. 1533-1536.

- [15] M. Nielsen and T. Larsen, "A transmitter architecture based on delta–sigma modulation and switch-mode power amplification," *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 54, pp. 735-739, 2007.

- [16] Y. Wang, "An improved Kahn transmitter architecture based on delta-sigma modulation," in IEEE MTT-S International Microwave Symposium Digest, 2003, pp. 1327-1330.

- [17] V. Bassoo, "A digital up-conversion architecture for future high efficiency wireless base stations," Victoria University, 2010.

- [18] V. Bassoo and M. Faulkner, "Sigma-delta digital drive signals for switchmode power amplifiers," *Electronics Letters*, vol. 44, pp. 1299-1300, 2008.

- [19] V. Bassoo, K. Tom, A. Mustafa, E. Cijvat, H. Sjoland, and M. Faulkner, "A Potential Transmitter Architecture for Future Generation Green Wireless Base Station," *EURASIP Journal on Wireless Communications and Networking*, vol. 2009, pp. 821-846, 2009.

- [20] H. Sjöland, C. Bryant, V. Bassoo, and M. Faulkner, "Switched mode transmitter architectures," in *Analog Circuit Design*, ed: Springer, 2010, pp. 325-342.

- [21] V. Bassoo, L. Linton, and M. Faulkner, "Analysis of distortion in pulse modulation converters for switching radio frequency power amplifiers," *Microwaves, Antennas & Propagation, IET*, vol. 4, pp. 2088-2096, 2010.

- [22] V. Bassoo, L. Linton, and M. Faulkner, "Analysis of Non-Uniform Polar Quantisers in a Sigma Delta Transmitter Architecture," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 59, pp. 3060-3070, 2012.

### DS modulator for digital wireless architecture

| ORIGI | NALIT | YR | EPC | DR1 |

|-------|-------|----|-----|-----|

|       |       |    |     |     |

15%

|   | SIMILARITY INDEX  PRIMARY SOURCES                                                                 |                       |  |  |

|---|---------------------------------------------------------------------------------------------------|-----------------------|--|--|

| 1 | link.springer.com Internet                                                                        | 64 words — <b>3</b> % |  |  |

| 2 | journal2.um.ac.id                                                                                 | 40 words — <b>2</b> % |  |  |

| 3 | ispg.ucsd.edu<br>Internet                                                                         | 35 words — <b>1</b> % |  |  |

| 4 | www.semanticscholar.org                                                                           | 34 words — 1 %        |  |  |

| 5 | Analog Circuit Design, 2010.  Crossref                                                            | 19 words — <b>1%</b>  |  |  |

| 6 | hal.archives-ouvertes.fr                                                                          | 19 words — <b>1</b> % |  |  |

| 7 | linknovate.com Internet                                                                           | 16 words — <b>1</b> % |  |  |

| 8 | V. Bassoo, L. Linton, M. Faulkner. "Analysis of Non-<br>Uniform Polar Quantisers in a Sigma Delta | 15 words — <b>1</b> % |  |  |

Transmitter Architecture", IEEE Transactions on Circuits and Systems I: Regular Papers, 2012 Crossref

Faulkner, M., V. Bassoo, H. King, and S. Sirmayanti. 8 words —

$$<1\%$$

"Baseband tuning of Cartesian delta-sigma RF upconverters", Electronics Letters, 2014.

$_{8 \text{ words}}$  -<1%Wonhoon Jang, Rui Cordeiro, Arnaldo Oliveira, Nuno Borges Carvalho. "A Broadband Almost-Digital RF Transmitter With an Efficient Power Amplifier", IEEE Transactions on Microwave Theory and Techniques, 2016 Crossref

- $_{8 \text{ words}}$  -<1%aast.edu Internet  $_{8 \text{ words}}$  -<1%epdf.tips 8 words = < 1%prism.ucalgary.ca 20  $_{8 \text{ words}}$  -<1%zapdf.com Internet  $_{6 \text{ words}}$  - < 1%"Sigma-Delta Converters", Wiley, 2018 Crossref

- $_{6 \text{ words}}$  < 1 %V. Bassoo, K. Tom, A.K. Mustafa, E. Cijvat, H. 23 Sjoland, M. Faulkner. "Potential Architecture for Future Generation `Green' Wireless Base Station", 2009 4th International Symposium on Wireless Pervasive Computing, 2009

Crossref